Direct Memory Access Technique: Explanation

Introduction

Direct Memory Access, or DMA, is a technique for moving data from RAM to another area of the computer without first processing it with the CPU. While the CPU processes the majority of the data your computer inputs or outputs, certain data doesn't need to be processed or can be handled by a different device.

DMA is a quicker and more effective means to transfer data from the computer's memory to external devices in these circumstances. Devices must be allocated to a DMA channel in order to use direct memory access. Every connected device can be given a different set of DMA channels by the port type on a computer.

For instance, a sound card might require access to data kept in the computer's RAM, but since it has the ability to process the data, it might use DMA to avoid the CPU. DMA-capable video cards may also access system memory and process visuals without a CPU. Compared to older hard drives that required the data to be processed by the CPU first, ultra DMA hard drives employ DMA to transport data more quickly.

The Programmed Input/Output (PIO) interface, an alternative to DMA, requires the processor to handle all data transfer between devices. Ultra DMA, a more recent protocol for the ATAIIDE interface, offers a burst data transmission rate of up to 33 mbps. Additionally, PIO modes 1, 3, and 4 as well as multiword DMA mode 2 at 16.6 mbps are supported by hard drives that ship with Ultra DMAl33.

DMA Transfer Types

Memory to Memory Transfer

This approach involves moving a block of data from one memory address to another. The data byte from the source address is loaded into the DMA controller's temporary register in this mode, and in the subsequent transfer cycle, the data from the temporary register is stored in the memory pointed by the destination address. In this mode, the current address register of channel 0 is used to point the source address and the current address register of channel 0 is used to point the destination address. Current address registers are incremented or decremented after each data transmission depending on the parameters at the time. Additionally, after each data transfer, the channel 1 current word count register is decremented by 1 as well. When channel 1's word count reaches FFFFH, a TC is produced that triggers the EOP output and ends the DMA service.

Auto initialize

In this mode, the microprocessor concurrently loads the current address and word count registers with the base address and word count registers during initialization. Throughout the whole DMA service, the address and the count in the base registers stay constant. The initial values of the current address and current word count registers are automatically restored from the base address and base word count register of that channel following the first block transfer, or after the activation of the EOP signal. The channel is prepared to perform another DMA service after auto startup without CPU assistance.

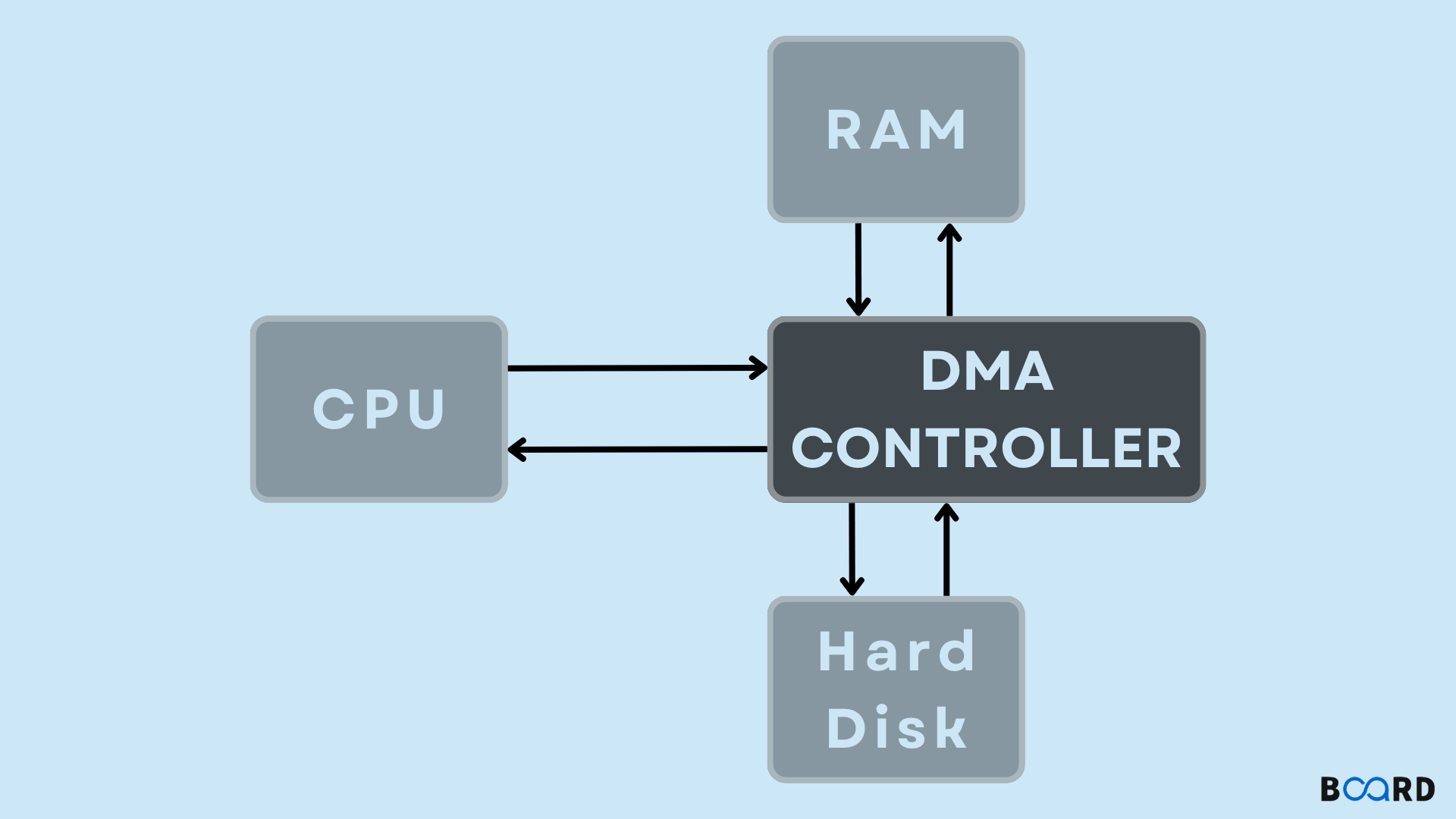

DMA Controller

The controller, which controls all DMA data transfers, is built inside the processor board. There are two processes involved in transferring data between system memory and a 110 device. The DMA controller receives data from the sending device, which then sends it to the receiving device. The DMA controller receives information from the microprocessor about the source, target, and volume of data that has to be sent. The data is then transferred by the DMA controller, freeing up the microprocessor to work on other processing duties. When a device wishes to send or receive data over the Micro Channel bus, it must compete with all the other devices vying for control of the bus. Arbitration is the name of this procedure. Instead, the I/O device that is delivering or receiving data (the DMA slave) engages in arbitration for control of the BUS, not the DMA controller. But when the central arbitration control point agrees to the DMA slave's request, the DMA controller takes over the bus.